Difference between revisions of "OZY"

(remove dead link, frame and reposition picture) |

(frame block diagrams, move up, remove section head) |

||

| Line 1: | Line 1: | ||

| − | + | '''OZY'''mandias - HPSDR Host Interface & Control | |

| − | + | [[Image:Ozy_12_Feb_2007.jpg|thumb|500px]] | |

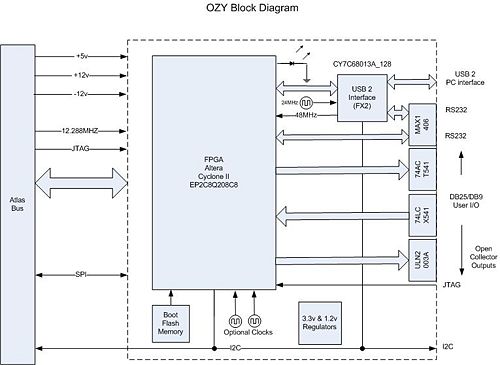

| + | The OZY module is an FPGA based interface controller card that provides the input and output connections to the real world. The use of an [[Altera Cyclone FPGA|Altera Cyclone II FPGA]] provides numerous control lines for interfacing the various boards connected to the Atlas backplane. | ||

The OZY was designed by Philip Covington [mailto:p.covington@gmail.com], N8VB. | The OZY was designed by Philip Covington [mailto:p.covington@gmail.com], N8VB. | ||

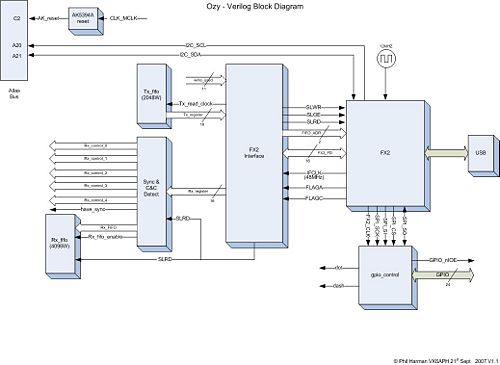

| − | + | [[Image:Ozy_Verilog.jpg|thumb|500px|Block diagrams of the OZY [[Verilog]] code]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | [[Image: | + | |

| − | + | ||

| − | Block diagrams of the OZY [[Verilog]] code | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

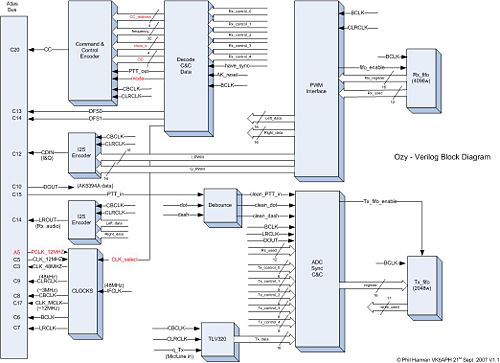

| + | [[Image:Ozy_Verilog2.jpg|thumb|500px]] | ||

OZY also provides a high speed USB 2.0 interface to the controlling PC. The USB interface uses a Cypress FX2 chip [http://www.cypress.com/portal/server.pt?space=CommunityPage&control=SetCommunity&CommunityID=209&PageID=259&fid=14&rpn=CY7C68013A] which greatly simplifies the design, development time and effort. The FX2 supports full duplex USB communications at > 30MB/s, which should allow sufficient bandwidth for current and future requirements. | OZY also provides a high speed USB 2.0 interface to the controlling PC. The USB interface uses a Cypress FX2 chip [http://www.cypress.com/portal/server.pt?space=CommunityPage&control=SetCommunity&CommunityID=209&PageID=259&fid=14&rpn=CY7C68013A] which greatly simplifies the design, development time and effort. The FX2 supports full duplex USB communications at > 30MB/s, which should allow sufficient bandwidth for current and future requirements. | ||

| Line 25: | Line 15: | ||

Whilst specifically designed to support the various HPSDR modules the OZY board makes an excellent general purpose FPGA development system. The source code to both the FX2 and FPGA software is available under GPL and the board is very cost competitive compared with other FPGA development systems. | Whilst specifically designed to support the various HPSDR modules the OZY board makes an excellent general purpose FPGA development system. The source code to both the FX2 and FPGA software is available under GPL and the board is very cost competitive compared with other FPGA development systems. | ||

| − | |||

The latest schematic, PCB and BOM of the OZY board can be found at: http://openhpsdr.org/support.html | The latest schematic, PCB and BOM of the OZY board can be found at: http://openhpsdr.org/support.html | ||

| Line 31: | Line 20: | ||

OZYMANDIAS??? See http://en.wikipedia.org/wiki/Ozymandias | OZYMANDIAS??? See http://en.wikipedia.org/wiki/Ozymandias | ||

| − | + | ==History== | |

| − | + | ||

| − | + | ||

| − | + | ||

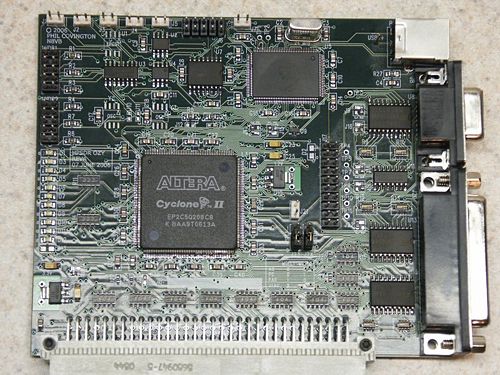

| + | [[Image:OZY_PROD1.jpg|thumb|500px|First production board, 5 April 2007]] | ||

9/22/2007: Architecture Changes | 9/22/2007: Architecture Changes | ||

| Line 54: | Line 41: | ||

08/15/2006: All Alpha OZY boards are now working. The Janus FPGA code has been ported and is working correctly. Phil, VK6APH, had the first QSO using the OZY + Janus + Atlas combination on 12th August 2006. Check out of all the I/O functions continues. | 08/15/2006: All Alpha OZY boards are now working. The Janus FPGA code has been ported and is working correctly. Phil, VK6APH, had the first QSO using the OZY + Janus + Atlas combination on 12th August 2006. Check out of all the I/O functions continues. | ||

| − | [[Image:PICT1713 08.jpg| | + | [[Image:PICT1713 08.jpg|thumb|500px|Assembled OZY as of 14 July 2006]] |

07/20/2006: OZY Utilities are written to allow firmware download and FPGA upload via USB using libUSB. A C# class library was written to allow the use of libUSB with C# programs and IronPython. | 07/20/2006: OZY Utilities are written to allow firmware download and FPGA upload via USB using libUSB. A C# class library was written to allow the use of libUSB with C# programs and IronPython. | ||

Revision as of 14:17, 31 May 2009

OZYmandias - HPSDR Host Interface & Control

The OZY module is an FPGA based interface controller card that provides the input and output connections to the real world. The use of an Altera Cyclone II FPGA provides numerous control lines for interfacing the various boards connected to the Atlas backplane.

The OZY was designed by Philip Covington [1], N8VB.

OZY also provides a high speed USB 2.0 interface to the controlling PC. The USB interface uses a Cypress FX2 chip [2] which greatly simplifies the design, development time and effort. The FX2 supports full duplex USB communications at > 30MB/s, which should allow sufficient bandwidth for current and future requirements.

The FPGA also provides the necessary control logic and data formatting for the Janus board as well serial and parallel interfaces for user defined I/O.

Whilst specifically designed to support the various HPSDR modules the OZY board makes an excellent general purpose FPGA development system. The source code to both the FX2 and FPGA software is available under GPL and the board is very cost competitive compared with other FPGA development systems.

The latest schematic, PCB and BOM of the OZY board can be found at: http://openhpsdr.org/support.html

OZYMANDIAS??? See http://en.wikipedia.org/wiki/Ozymandias

History

9/22/2007: Architecture Changes

Sync detect and C&C decode now done at the output of the FX2 rather than the Rx FIFO output. This ensures we can control other cards on the Atlas bus in the event that not all clocks are fully defined. This change is necessary so that we can select the 10MHz reference clock from Gibraltar, Penelope or Mercury and also the 125MHz reference from Penelope or Mercury. Numerous code tidied up and comments updated. The Verilog diagrams have been updated to reflect the changes.

2/11/2007: Ready for production.

12/10/2006: Initial tests of Ozy V2 indicate all functions are OK - VK6APH.

11/30/2006: All Alpha 2 kits arrived (including VK6APH in Oz).

11/20/2006: All Alpha 2 kits shipped.

11/18/2006: The parts for the Alpha 2 release are in hand and kitted for the test team. The PCBs were shipped today via overnight service, and should arrive Monday, Nov 20. With luck, all Alpha 2 kits should be enroute to the testers the same day.

10/06/2006: The schematic and PCB board layout for REVB of OZY is complete. This revision corrects issues we found in OZY REVA alpha 1 boards. See OZY_REVA_ALPHA_REVLIST for issues that were corrected.

08/15/2006: All Alpha OZY boards are now working. The Janus FPGA code has been ported and is working correctly. Phil, VK6APH, had the first QSO using the OZY + Janus + Atlas combination on 12th August 2006. Check out of all the I/O functions continues.

07/20/2006: OZY Utilities are written to allow firmware download and FPGA upload via USB using libUSB. A C# class library was written to allow the use of libUSB with C# programs and IronPython.

07/10/2006: OZY now has firmware! Work is under way to switch to libUSB instead of the Cypress driver.

07/07/2006: OZY has been completely assembled minus two components, the Dallas serial to 1-Wire converter and a diode on the logic analyzer port (parts on backorder -estimated ship date 07/07/2006). The Cypress CY7C68013A (FX2) enumerates on USB. The I2C EEPROM on board was programmed with a C0 load with VID 0xFFFE and PID 0x0007. The CyUSB.sys driver's inf file was modified to include the VID/PID. Later the LibUSB-Win32 driver will be used instead. The Cyclone II FPGA was loaded with a test program via JTAG and the test program was successfully run. The next task is to load firmware into the FX2 to allow downloading of the FPGA code over USB.

See OZY_REVA_ALPHA_REVLIST for proposed additions/changes to the OZY design before it is released for production.

See OZY_REVA_STARTUP for notes/issues on debugging/startup of the OZY alpha board.