HERMES

Hermes - A DUC/DDC Transceiver

Project Leader: Kevin M0KHZ

Following the outstanding success of Mercury and Penelope, and while investigating the verilog code for both, I had the insane idea of merging the verilog code of Mercury and Penelope into a single fpga! I played around with this idea for a while and the more I thought about it the more I liked the idea.

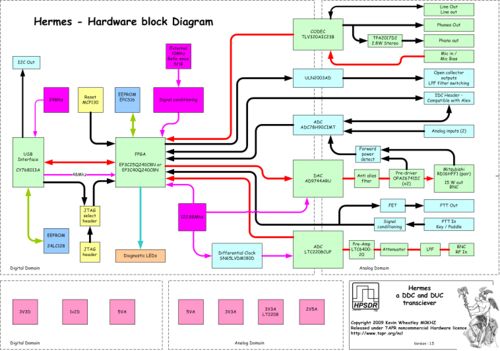

So here is the proposal, to develop a single board HPSDR based on the hardware of Mercury and Penelope and a single large fpga.

This board would have PC connectivity by USB. I’m planning to squeeze this all onto Euro Card sized PCB (100 x 160 mm), and if I utilize both sides I might even have room for a Pennywhistle type PA :).

Basic specs so far (nothing cast in stone)

- Fpga EP3C25Q240C or EP3C40Q240 (I think this is the largest without BGA pin out)

- Mercury receive chain

- Penelope transmit chain, possible small change to gain distribution

- USB2 to PC data transfer

- Pennywhistle PA (if there’s room)

- 10Mhz ext an option

- Alex filter switching header

- 2.8W stereo audio PA

- 13.5V supply

Following the tradition of the HPSDR naming convention, I thought Hermes was appropriate as he was known for his invention and theft!

Current status ( 20 April 09 ), Project proposal open for comment. Looking to nail ‘major’ hardware decisions by the end of the month. Initial draft schematics will then be produced and placed here on the Wiki for comment.

Kevin – M0KHZ

Update ( 28 April 09 )

Since the announcement of the Hermes project there has been quiet a bit of traffic ‘in the background’, in summary the hardware details are now reasonably stable. What follows are some snippets of traffic to provide readers with some insight to the development process ......

Phil VK6APH has provided several suggestions, namely:

There needs to be an audio out from the TLV320. JTAG - the JTAG programming can come from the FX2, perhaps we have a standard JTAG header and jumpers to connect the relevant pins on the FX2 so we can use either? Need to show the LPF at the RF input. We could take the forward power from the 15w PA as well since I think there are enough spare inputs to read all we need. ICD header needs to connect to ADC78H90. If there are spare inputs should we bring them out - perhaps for use with an external amplifier etc? 122.88MHz clock directly feeds DAC. Phil is also trying to find a packaged LPF so we can get rid of the toroids on the DAC output. Add a header for I2C signals from the FX2 to control external equipment.

Graham KE9H has made an interesting suggestion regarding the gain distribution of the existing Penelope 1/2 W PA strip :

As far as the gain re-distribution to get the transmit frequency response flat out to 50 MHz, you basically change the transformer T3 from a TC4-1T to a TC1-1T (which will maximize linearity of the AD9744,) and add a second OPA2674 in series with the current OPA2674 OpAmp, and redistribute the gain between them. The current OPA2674 is being run at 24 dB gain, and is hitting gain-bandwidth limits around 30 MHz. With two in series, they would each be set for around 12 dB gain, and the combination should be flat well over 60 MHz.

Graham is also investigating the use of a THS6012 as a substitute PA, this provided a very clean output, at a higher level, a test board has been drafted and a few boards have been ordered to enable to testing. I’m not sure this chip will form part of Hermes as the supply requirements are beyond the current spec, but I guess the final decision will be made once the test results are in :)

While I’m discussing the PA strip, I must reiterate that the PennyWhistle PA is really just a dream for Hermes, I really don’t think there will be enough room on the board, however I will squeeze everything one first, and if there is room, PennyWhistle will be considered.

Graham has also suggested some form of audio PA be included, this has now been added to the hardware block diagram.

Scotty WA2DFI, has made several suggestions and between us we have now settled on some of the connecting hardware. To save board edge space a number of the connectors are now ‘stack’ connectors. Scotty has also made a good start on the schematics, I’m not going to provide a guesstimate for release for comment, mainly due to Scotties Dayton commitments, but it’s going to be weeks not months :)

Phil N8VB has provided some valuable information, namely:

Take a look at how I connect the FX2 to the FPGA using port E for 8 bit parallel configuration. After configuration I use this as the 8 bit communications bus between the FX2 and the FPGA. This allows faster configuration of the FPGA and faster read/writing to the registers in the FPGA (especially for tuning word). You might want to use this scheme in Hermes.

Also, instead of using an Altera configuration device (especially for the larger '40 Cyclone III), consider using a SD card which can have a serial interface to the FX2. The FX2 can read the SD card and configure the FPGA via the parallel mode mentioned above.

Phil’s advice regarding the use of port E will be incorporated in Hermes. The move to an SD card is still in the balance as board real-estate is of a premium and I don’t understand / can’t see any benefits for the change? Can someone out there enlighten me?

Phil N8VB, has also enlightened me on capability of the FX2 (although I’ve had to delve into the technical reference and ‘Google’ to ‘partially’ understand USB end points):

The FX2 has 4 high speed endpoints. This is enough for full duplex operation of the receiver and transmitter via USB.

The current command and control scheme will need to be restructured to achieve this and is well worth pursuing.

Well I guess that pretty well brings everyone up to date with the Hermes story so far, so in summary, the hardware is close to being finalized, Scotty has made a start on the schematics, and I’m climbing the learning curve of OrCAD, in preparation to layout the board :)

Kevin - M0KHZ