Difference between revisions of "Janus"

(→Introduction) |

|||

| Line 16: | Line 16: | ||

[[Image:Janus.jpg]] | [[Image:Janus.jpg]] | ||

| + | |||

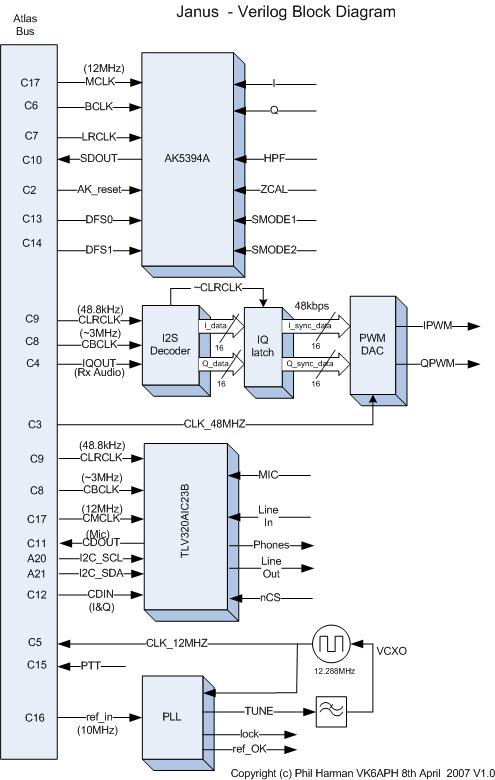

| + | Block diagram of the Janus Verilog code | ||

| + | |||

| + | [[Image:Janus_Verilog.jpg]] | ||

== Current Status == | == Current Status == | ||

Revision as of 04:08, 8 April 2007

Contents

JANUS - ADC/DAC Board

The project leaders for the board are Bill Tracey, KD5TFD and Phil Harman, VK6APH. Lyle Johnson, KK7P did the PCB layout.

Introduction

The Janus module is a very high performance, dual, full duplex, A/D and D/A converter board. The A/D sample rate options are 48, 96 or 192kHz and the D/As are fixed at 48kHz. While the M-Audio Delta 44 has become the de-facto standard for A/D sound cards for use with a SDR, there are a number of advantages to rolling your own. These include having complete control of any software drivers needed to communicate with the A/D chips as well as optimization of sampling rates and bit depths for individual signals. It's also possible to cost effectively develop a board which approaches the performance of professional high end sound cards.

Independent testing of the Beta Janus boards has confirmed the very high performance of the completed card.

The Janus board needs to be paired with an Ozy board in order to provide a high performance sound card replacement. This combination enables a single USB connection to provide all audio connections to the SDR hardware as well as acting as a parallel port replacement for the Flex-Radio SDR1000 (TM).

The consumer demand for high quality PC sound cards has resulted in the availability of a number of very high performance, and low cost, A/D and D/A converter chips that are ideal candidates for this project.

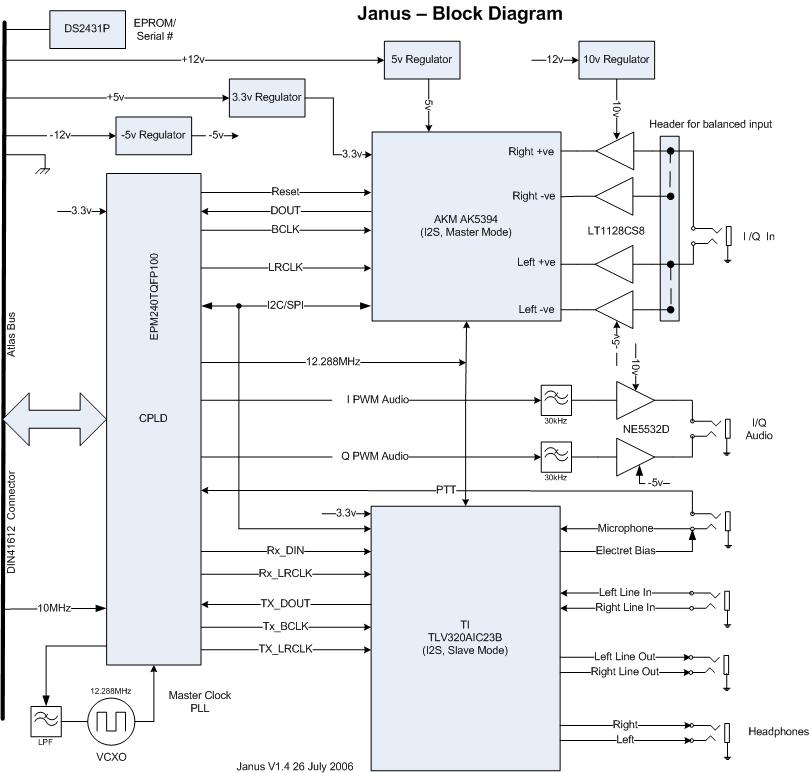

A block diagram of Janus is shown below.

Block diagram of the Janus Verilog code

Current Status

February 14 2007 - Production schematic files now at http://www.hamsdr.com/personaldirectory.aspx?id=501 and production BOM file now at http://www.hamsdr.com/personaldirectory.aspx?id=502. Only change from previous version is change of 2K resistors to 10K resistors for PWM input filter. KK7P

Feburary 12 2007 - Design released for production. VK6APH & KK7P.

February 01 2007 - Production PCB files now at http://www.hamsdr.com/personaldirectory.aspx?id=485 Minor changes to improve manufacurability. KK7P

January 29 2007 - uploaded 2006 ARRL/TAPR DCC paper on Janus: Media:Janus-DCC-2006-paper.pdf

December 23 - Updated (production!) PCB files now at (link deleted, see Feb 01 2007 ). Includes solder paste layer, minor tweaks to silkscreen layer and better separation of vias from SMT pads to facilitate automated assembly (and helpful for those of you who use toaster ovens to solder your boards!). KK7P

December 10 - Janus V2 tested with Ozy V2, all appears to work OK. VK6APH

November 21 - Initial check out of Alpha 2 board indicates all functions work OK. VK6APH

November 18 - Photo of Janus updated with Alpha 2 board. All kits are confirmed in the hands of the test team. KK7P

November 10 - PCBs arived early (thanks, FedEx!) and Alpha 2 kits were shipped today, Nov 10th. KK7P

November 09 - Alpha 2 PC boards were shipped yesterday, due to arrive Monday 13th. Alpha 2 test kits are ready to ship upon arrival of PC boards. Updated PCB files are now on hamsdr and pointed to by the corrected link below (status dated October 1st). KK7P

October 29 - Alpha board testing is complete!!! Thankyou to Bill, Bob and Rick. Alpha 2 PC boards were ordered today, with expected delivery early next week.

October 20 - Uploaded some screen shots comparing the pricey LT1128CS8 op amps compared to the more value priced NE5534ADR op amps Lyle (KK7P) suggested. Details are on OpAmp Bakeoff

October 1st - Janus Alpha 2 prototyping is underway. Parts have been ordered for six (6) boards. The changes outlined in the "Janus Alpha Revisions" (below) have been incorporated. The changes have all been tested by hacks on one or more of the original Janus boards. There is a small but significant test yet to be done, after which we will get the new PCB fabricated (assuming the remaining test is successful, of course).

See (link deleted, see Feb 14 2007 ) for the latest schematic (rev XC9).

See (link deleted, see Feb 14 2007 ) for the latest Bill of Materials(rev XC9).

August 15th - Janus has been successfully interfaced to the Ozy board. Currently preparing for Beta version prior to production.

July 14 2006 - All the functions have been tested successfully! The sampling speed (48/96/192k) can be changed from PowerSDR now. Minor changes to the circuit and PCB are being made ready for the production version. The main clock at 12.288MHz has been changed to a VCXO so it can be phase locked to the Mercury reference.

July 13 2006 - See (link deleted, see Feb 14 2007 ) for provisional Janus Beta schematic.

July 08 2006 - See JanusAlphaRevisions for some notes on revisions needed for the production Janus board.

Update June 21 - All parts are in hand or on the way to alpha builders, and the bring up begins. More info on the bring up of the Apha Janus @ JanusBringup --kd5tfd.

Update June 07 - Alpha PCBs arrived today! - KK7P

Update 26 May 2006

The results of the ADC bake-off are in and the AK5394A is the clear winner for our particular application due to its flat noise floor at 192kps.

The measured figures of the prototype Janus using the AK5394A are:

Noise Floor = -160dBm (in an 11Hz FFT bandwidth) Dynamic Range = 120dB ENOB = 20 bits

We are now at the final review stages of the Janus circuit and expect to be moving to prototype PCB manufacture very shortly.

The Verilog code for the Xylo board has been changed to support the AK5394A ADC in I2S Slave mode. In addition, the ADC can be switched between 192/96/48kps under control of PowerSDR. The clocking for the TLV320 has been altered so that its ADC and DAC always run at 48kHz. The TLV320 code has also been altered to enable it to run in I2S mode. The clocks for the ADC and DAC are now obtained by dividing down the 24.576MHz rather than running the AK5394A in Master mode.

Bill, KD5TFD, has modified PowerSDR so that it can accept ADC data from the AK53954A at 192/96/48kps and send received DAC data back to the TLV320 at 48kHz. He has also modified the code to up-sample the 48kHz microphone/line-in data from the TLV320 to 192/96kps.

Bill's modifications to the PowerSDR sofware provides 3 A/D inputs ( I, Q, and line/microphone) and 4 outputs (left/right receiver audio and I/Q audio for the exciter). These are both full duplex so VOX etc. operation works just fine. He has also added PTT and CW inputs to the FPGA and these appear to provide very low latency inputs to PowerSDR.

The document that describes the protocol used over the USB to/from the PC can be found below in the documentation section for JANUS.

Phil, VK6APH

The PCB for the Janus board was laid out by Lyle, KK7P. The latest version of the Alpha schematic may be found at (link deleted, see Feb 14 2007 ) and the PCB layout is at (link deleted, see Feb 01 2007 ) for viewing or download.

Note that the PCB follows Phil Covington's 120mm x 100mm suggestion. Minor edits have been made to the schematic to incorporate the latest changes from Phil Harman.

You will note that copyrights have been asserted to both the schematic and the PCB layout. This is to protect the content while we figure out how to make this open source. Some of us have had the unpleasant experience in the past of a third party taking our work, claiming it as their own, and then demanding compensation! Note that there is no guarantee that this design does not infringe on someone's patents, designs or claims; use it at your own risk.

A photograph of the first assembled Alpha 2 board (11/18) is here:

The selection of A/D converter for microphone and line inputs and D/A converters for audio out and I/Q signals for the transmitter was somewhat simpler. It was hard to go past the TI TLV320AIC23B. This remarkable chip contains a microphone amplifier, with bias feed for an electret microphone, stereo line in and out, stereo 16-bit A/D and D/A converters together with 35mW stereo headphone amplifier. The price for this chip is $7 (US) in single quantities. We have a lot to thank MP3 players for!

Circuit Description

This description applies to the Rev XC11 schematic, released February 14, 2007.

Sheet 1 - BUS INTERFACE and CPLD

The 96-pin DIN connector which plugs into the ATLAS backplane is in the upper left of the page, labeled P1A..P1C.

U11 is an Altera EPM240 CPLD. [1] This is actually a small, SRAM-based FPGA similar to the Cyclone series. It has an on-chip Flash configuration memory. U11 is used to map the ATLAS buses to the ADC, CODEC and PWM on Janus. It also provides clocks to the ADC and CODEC, derived from XO1, or accepts an external clock if multiple Janus boards are installed. Three unused pins on the device are used for a test point (TP3) and to drive a pair of LEDs (LED4, LED5) under program/CPLD control.

XO1 is a voltage controlled crystal oscillator. A digital phase locked loop is implemented in the CPLD, and the resistors and capacitors associate with the TUNE line going to XO1 pin 1 are used to filter the pulses from the CPLD to a DC voltage. Initial experiments show a lock time on the order of 15 seconds. The intent is to slave this crystal oscillator a very stable reference (see the Gibraltar project, for example), so a slow response with very low noise is prefered to a fast response with noisy sidebands.

P2 allows local configuration of U11 by a standard Altera-compatible JTAG programmer. U11 may also be programmed over the ATLAS bus by another device, such as Ozymandias. For the latter, JP12 must be placed if Janus is the last card from the master. There must be no empty slots beween Ozymandias and Janus for this to work, and Ozymandias must be "upstream" from Janus. If all slots are filled, then the "upstream" requirement is no longer in force.

An I2C interface is provided to configure the CODEC (on sheet 3) as well as to the CPLD if an I2C function is programmed into it. JP10 and JP11 may be placed to directly conenct the CODEC to the ATLAS I2C bus pins. R34 and R37 are local pull ups to enable to I2C open-collector logic.

U13 [2] provides a unique 64-bit serial number as well as 128 bytes of EEPROM memory on a Dallas 1-wire bus. This is to support remote identification and configuration of Janus, for example by Ozymandias.

RP1-6 provide a statis bleed-off path to protect Janus' circuitry from damage when the board is inserted into a backplane, and from undriven inputs.

Sheet 2 - ADC

U7 is the AKM AK5394A ADC chip. [3] This is a 2 channel, 24-bit component with excellent specifications and capable of operation beyond 200 kilosamples/second. Significant bypassing is required on various pins of this device.

U2 provides bias voltage for the input buffer amplifiers, and R10 is selected to match the buffer amplifier offset to the ADC inputs.

There are two channels of input amplifer, the left is discussed, the right is similar.

Assuming a balanced input applied to J2 (external cable) or P3 (adjacent board), one side is coupled through FL3 to U4. FL3 helps to isolate noise on the input, perhaps stray RF. R22 introduces DC bias, C26 couples the audio signal. U4 buffers the signal, with R19, R21 and C2 arranged to maximize dynamic range and minimize noise. The other side of the balanced input signal is similarly buffered by U6.

This input configuration was chosen for high input impedance to minimize loading on a QSD-style detector that might drive Janus. This circuit is not compatible with "professional audio" signal levels or impedance.

U6/U4 outputs are bypassed by C22, working in conjunction with R19/R21/R25/R26 to provide rolloff for the sigma-delta ADC convertor within U7.

If an unbalanced signal is required, then jumpers JP4 and JP6 are placed. The input signal is applied to U4, and the output from U4 is coupled to the inverting input of U6 through R23/JP6 so that U6 provides inverting, unity gain. The non-inverting input of U6 is shunted by JP4.

If a higher level signal input tolerance is required, JP5 is removed and R17 reduces the input ampltitude, working against the nominal input impedance of the buffer amplifier.

Sheet 3 - CODEC and PWM

U9 is a TI TLV320AIC23B [4] 2-channel CODEC (COder/DECoder) which has ADC and DAC functions. It is fully configured by the FPGA. Signals are bypassed for RF and AC coupled to the analog inputs or from the analog outputs of U9. U9 is intended to provide "baseband" audio I/O for the HPSDR. Note that no speaker amplifier is provided on Janus.

Just as 8-pin microphone connectors adhere to no standards in Amateur radio, simple 3.5mm microphone connectors are also "standards free." JP7..JP9 allow configuration of the microphone connector. JP7 may be placed to apply DC bias to the tip or ring of the mic connector, or left off if no bias is required (e.g., a dynamic mic). JP8 selects the tip or ring for PTT, or may be left off if the mic has no PTT function. JP9 selects the tip or ring for mic audio. This jumper must be placed!

The PTT signal is pulled high by R35, and the PTT assertion (pulled to ground) is coupled by D1. R33 and C58 provide further decoupling of the PTT input.

U14 provides integration and buffering of the PWM signals from Ozy or some other source on the ATLAS backplane. These outputs are intended to drive a QSE mixer for transmission.

Sheet 4 - Power Supply

U12 and associated bypass capacitors supply +3V3. This is the primary digital power supply, as well as the CODEC analog supply.

U8 is the +5V regulator, which is used by the AKM AK5394A ADC on sheet 2.

U5 supplies +10V, used in the ADC, PWM and CODEC analog buffer amplifiers.

U10 provides -5V, used by the ADC analog buffer amplifiers.

Four (4) LEDs are visual indicators that the various supplies are working.

J8 is an optional terminal strip connector to simplify powering Janus if the Atlas backplane is not present.

Preliminary Parts List

The parts list for Rev XC9 of Janus in Excel format is here: (link deleted, see Feb 14 2007 )

* The Verilog sofware for the FPGA is being written using the free web version of Altera's Quartus II V6.1 software

Documentation

There are two parts of the written documentation in planning. Part #1 documents the schematic as well as the USB protocol for JANUS. Part #2 shows the board assembly as well as additional information.

Part #1 is available at: http://www.needles.de/HPSDR/JANUS_1_DocuUSLet.pdf

Part #2 will be available soon.