Difference between revisions of "METIS"

| Line 54: | Line 54: | ||

- Proving difficult to source in the leaded version at the moment | - Proving difficult to source in the leaded version at the moment | ||

| + | |||

| + | |||

| + | By using a large FPGA if offers the potential to add a soft core microprocessor in the future so that the board can run a full TCP/IP stack, UDP etc. | ||

| + | |||

| + | e.g. uIP http://www.sics.se/~adam/uip/index.php/Main_Page | ||

| + | |||

| + | Initially we will use the Gigabit PHY as just a fast connection to the PC and use raw frames to communicate. | ||

| + | |||

Revision as of 19:04, 16 July 2009

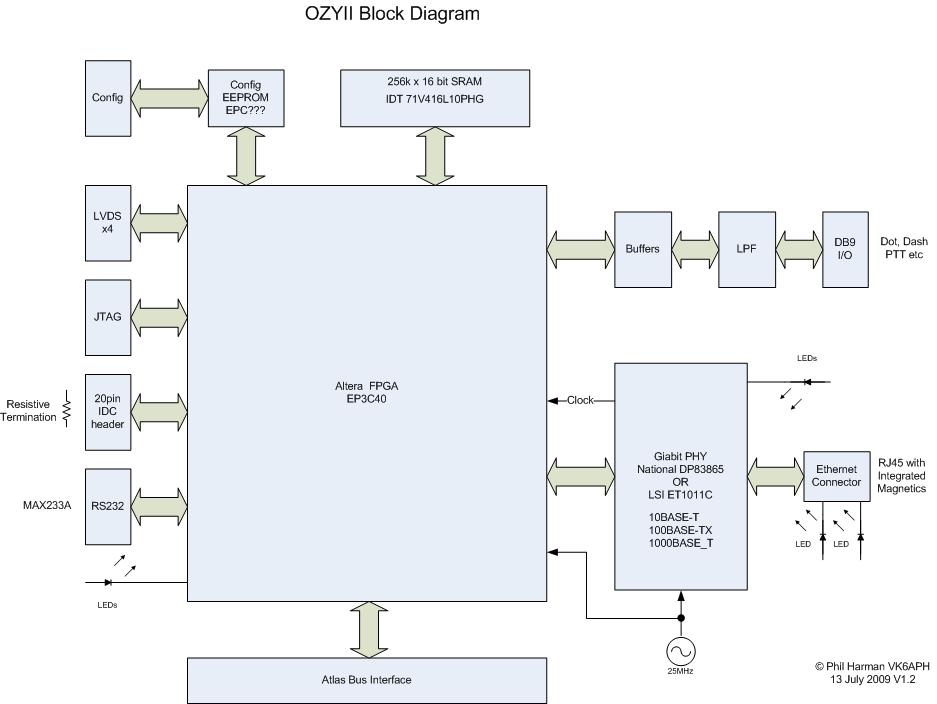

OzyII (or maybe Aussie II?) will be a high speed PC interface. Whilst the original Ozy board has served us well to date, in order to implement some of the future HPSDR projects we are going to need a faster interface between the various boards on the Atlas bus and the PC.

Aussie II is a kick off point for this project. Since this board will not need to support the SDR1000 there will be room for testing other high performance/speed interfaces.

Initial thoughts are around an Atlas size board that contains a large, leaded, Altera Cyclone III FPGA connected to a Gigabit Ethernet PHY.

User input relating to the design and features is requested via the HPSDR reflector.

Project Leader: Phil, VK6APH

17 July 2009

The following is a block diagram of a possible design for OzyII.

Since the project will be Open Source we have avoided PYH chips that require an NDA to obtain the data sheets. There are two PHY chips currently under consideration:

National DP83865

For

- Easily sourced

- Used by other SDRs so code base is available

- Good design and support tools from National

Against

- 4x the cost of the LSI ET1011C

- Power requirements - 750mW

- Needs multiple power supplies

LSI ET1011C

For

- Low cost

- Lower power

- Single power supply

Against

- Proving difficult to source in the leaded version at the moment

By using a large FPGA if offers the potential to add a soft core microprocessor in the future so that the board can run a full TCP/IP stack, UDP etc.

e.g. uIP http://www.sics.se/~adam/uip/index.php/Main_Page

Initially we will use the Gigabit PHY as just a fast connection to the PC and use raw frames to communicate.

Feedback and comments are requested via the HPSDR reflector.

Ethernet Notes:

In general, an Ethernet subsystem is divided into two parts: the media access controller (MAC) and the physical device (PHY or line interface). Generally, the MAC handles generating and parsing physical frames and the PHY handles how this data is actually moved to or from the wire. The PHY is just a means of transmitting raw bits rather than logical data packets over a physical link that are connecting network nodes.

Possible PHY devices ( non BGA or PCI interface, NDA not required)

- National DP83865 development kit - http://www.morethanip.com/boards_10_100_1000_dp83865.htm 500EUR + 100EUR postage

- reference design - http://www.national.com/appinfo/networks/files/dp83865_refdesign.pdf

- http://www.national.com/analog/interface/refdesign_demoboards - for Orcad files

Useful info:

http://www.techonline.com/article/pdf/showPDFinIE.jhtml?id=2088017281