OZY

OZYmandias - HPSDR Host Interface & Control

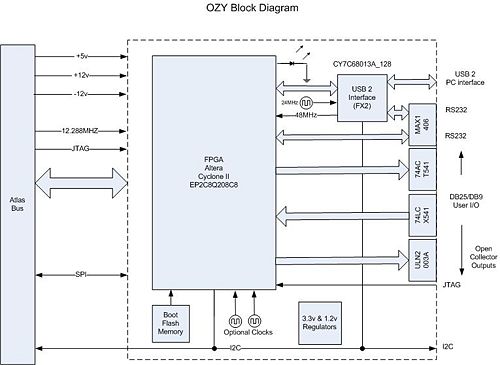

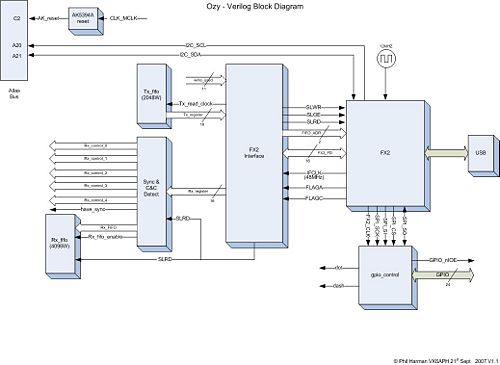

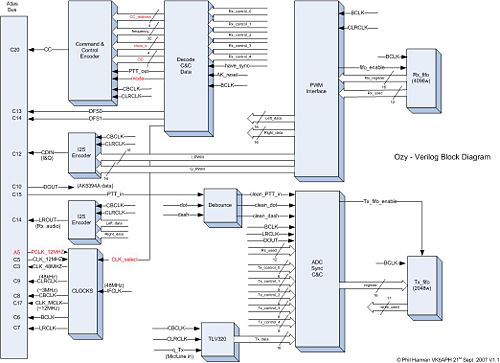

The OZY module is an FPGA based interface controller card that provides the input and output connections to the real world. The use of an Altera Cyclone II FPGA provides numerous control lines for interfacing the various boards connected to the Atlas backplane.

The OZY was designed by Philip Covington [1], N8VB.

OZY also provides a high speed USB 2.0 interface to the controlling PC. The USB interface uses a Cypress FX2 chip [2] which greatly simplifies the design, development time and effort. The FX2 supports full duplex USB communications at > 30MB/s, which should allow sufficient bandwidth for current and future requirements.

The FPGA also provides the necessary control logic and data formatting for the Janus board as well serial and parallel interfaces for user defined I/O.

Whilst specifically designed to support the various HPSDR modules the OZY board makes an excellent general purpose FPGA development system. The source code to both the FX2 and FPGA software is available under GPL and the board is very cost competitive compared with other FPGA development systems.

The latest schematic, PCB and BOM of the OZY board can be found at: http://openhpsdr.org/support.php

NOTE: Ozymandias is no longer available from TAPR.

OZYMANDIAS??? See http://en.wikipedia.org/wiki/Ozymandias_(name)