Difference between revisions of "PENELOPE"

From HPSDRwiki

| (49 intermediate revisions by 6 users not shown) | |||

| Line 1: | Line 1: | ||

| − | + | '''PENELOPE - Companion Exciter to Mercury''' | |

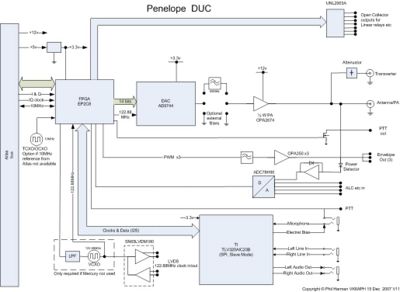

| − | + | [[Image:DUC-v11.jpg|thumb|400px|block diagram of the Penelope DUC]] | |

| + | The '''Penelope''' digital up converter (DUC) is a 1/2-watt transmitter/exciter board. It makes a good companion to the [[MERCURY|Mercury]] HF direct sampling receiver board. When connected to the [[ATLAS|Atlas]] (bus) it will process the I and Q signal from the personal computer. | ||

| − | + | The project leader for the board was Phil VK6APH with KK7P doing the PCB layout. | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ''NOTE: Penelope is being manufactured by Gerd, DJ8AY. It has also been superseded by [[Pennylane]] which is available from [http://www.iquadlabs.com iQuadLabs] | |

| − | + | [[Image:penny-5.png|thumb|300px|Wide band spurious output by John N8UR. Penelope producing 0.25w out on 14.1MHz]] | |

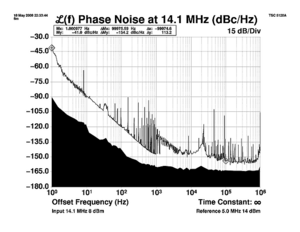

| − | + | [[Image:penny-spectrumplot.png|thumb|300px|Phase noise plot by John N8UR. Penelope producing 0.25w out on 14.1MHz and phase locked to on board 10MHz TCXO]] | |

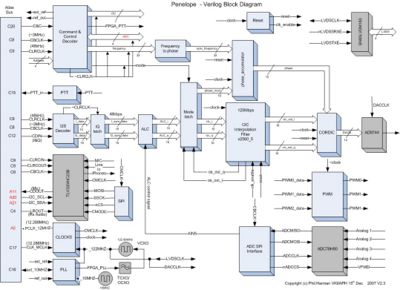

| − | + | [[Image:Penelope_Verilog.jpg|thumb|400px|Verilog block diagram]] | |

| − | + | == See Also == | |

| + | * [[Penelope - Development History]] | ||

| − | + | * [[Penelope - Manufacturing]] | |

| − | + | * [[Penelope - Trouble_Shooting]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| + | * [[Never Short a Penelope by AD9DP|Never Short a Penelope]] | ||

| − | + | [[Category:Penelope| ]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | [[ | + | |

Latest revision as of 11:49, 15 September 2011

PENELOPE - Companion Exciter to Mercury

The Penelope digital up converter (DUC) is a 1/2-watt transmitter/exciter board. It makes a good companion to the Mercury HF direct sampling receiver board. When connected to the Atlas (bus) it will process the I and Q signal from the personal computer.

The project leader for the board was Phil VK6APH with KK7P doing the PCB layout.

NOTE: Penelope is being manufactured by Gerd, DJ8AY. It has also been superseded by Pennylane which is available from iQuadLabs