EXPERIMENTERS-CORNER

This area is for discussing and stirring ideas that are not yet projects of HPSDR. If you would like to add to this area or edit existing material, please apply to the "Wiki Sysop" for log in authorization. Email "ae5k" at "openhpsdr" dot "org" and specifically mention the "Experimenters Corner" in your request. Please use courtesy and common sense in what you place here and remove old stuff no longer applicable or of interest. The Wiki Sysop reserves the right to edit or remove material deemed in his opinion not appropriate and to revoke log in authorization for any abusers.

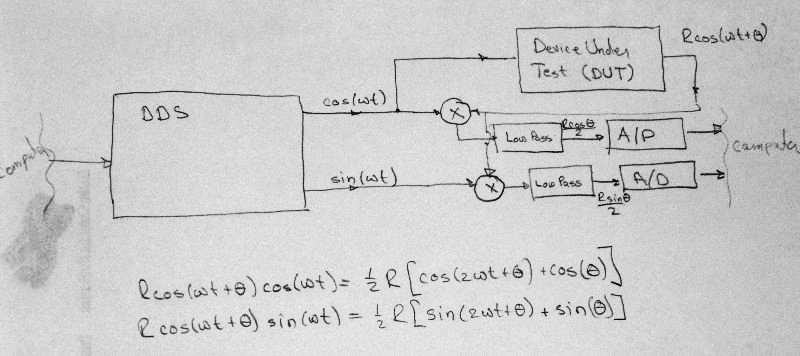

Vector Network Analyzer for Phoenix

The block diagram for the Phoenix is so similar to that of a vector network analyzer that it would be a shame if we didn't include that capability in the Phoenix.

The idea is that we want to measure the vector that is described by having a length R and angle theta. The low pass filters give us 1/2 R cos( theta ) and 1/2 R sin( theta ), which are the Cartesian coordinates of that vector, just what we want.

This is only a starting point for the block diagram. We need to do some thinking about how to best integrate it into the Phoenix without compromising the present goals of the Phoenix. Post your ideas here!

Artemis - A PIC based Web Server with lots of I/O to control

Project proposal block diagram:

Following advice from Lyle KK7P the proposed PIC is now a PIC32MX695F512L, more memory & 4 SPI ports and same cost :) Block diagram updated to reflect, see below:

Artemis_Block_Diagram_Rev_0_2.pdf

Lets talk terminal blocks... using double stacked screw terminal blocks simular to this:

Double_Stack_Terminal_Block.pdf we can achieve 36 connections to the outside world (18 x 18).

If we have any spare I/O (very probably) we could add an internal IDC connector or two. Or tripple stack the terminal blocks, providing 54 screw termainals, with something like this:

Tripple_Stack_Terminal_Block.pdf

Suggestions welcome.

Following correspondence with Jeremy NH6Z a revised PHY solution has been incorporated, Artemis can now function as a 4 port switch, for example, port 1 to network, port 2 to Metis, port 3 to Hermes, port 4 second Metis, port 5 (internal) to Artemis.

Block diagram updated to reflect, see below:

Artemis_Block_Diagram_Rev_0_3.pdf

Although comments from Chris and Lyle regarding an Atom CPU solution are clearly attractive, and inexpensive, I am still contemplating a PIC based solution (not much fun replicating an existing design - HI )

Please keep the ideas coming.